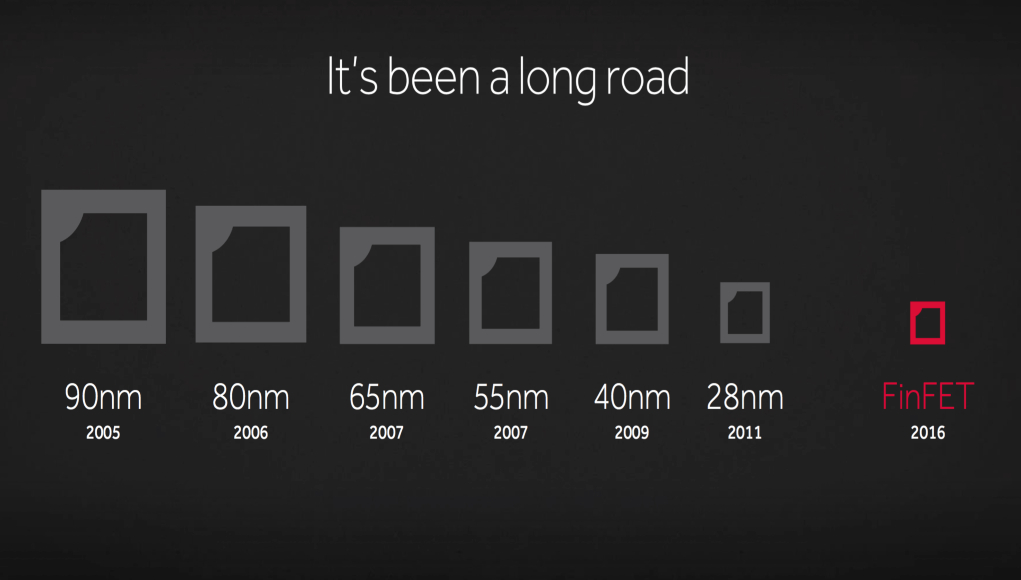

TSMC inicia la producción de chips con 7nm. TSMC anunció la semana pasada que había comenzado la producción de alto volumen (HVM) de chips utilizando su tecnología de proceso de primera generación de 7 nm (CLN7FF). El fabricante de semiconductores por contrato dice que tiene más de una década de clientes con decenas de diseños deseables de utilizar la tecnología para hacer sus circuitos integrados.

Índice de contenido

7nm

El nodo de 7 nm es un gran negocio para la industria de la fundición en general y TSMC en particular. Cuando se compara con la tecnología CLN16FF + (tecnología de proceso FinFET más utilizada de TSMC), CLN7FF permitirá a los diseñadores de chips reducir sus tamaños de matriz en un 70% (con el mismo número de transistores), reducir el consumo de energía en un 60% o aumentar la frecuencia en un 30% (a la misma complejidad). Hasta el momento, TSMC ha pegado 18 productos de clientes utilizando la tecnología CLN7FF, más de 50 productos CLN7FF se grabarán a finales de 2018.

Una diferencia del CLN10FF de TSMC, que se usa para un número limitado de clientes para un número limitado de SoC móviles, se espera que el CLN7FF se use para CPU, GPU, FPGA, procesadores de redes neuronales, aceleradores de criptomonedas, SoC móviles , etc. Esto es importante porque la demanda de teléfonos inteligentes se está desacelerando y TSMC necesita que otros clientes compensen los pedidos más bajos de SoC móviles.

"Hasta ahora, ya hemos favorecido a más de 18 productos de clientes con buen rendimiento [y] rendimiento", dijo CC Wei, Co-CEO y Presidente de TSMC, durante una conferencia telefónica con analistas financieros. "A finales de este año, se han planificado más de 50 productos de cintas de salida para aplicaciones en dispositivos móviles, CPU de servidores, procesadores de red, juegos, GPU, PGA, criptomonedas, automotrices e IA. Nuestro 7nm ya está en producción en volumen ".

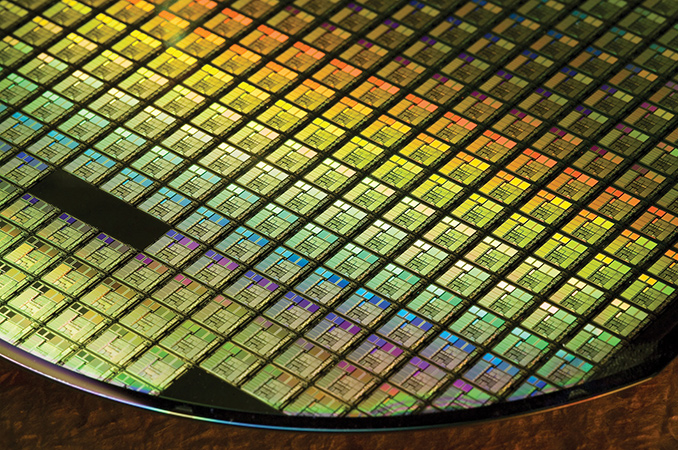

La tecnología de proceso CLN7FF de TSMC se basará en la litografía ultravioleta profunda (DUV) con láser excímeros de argón fluoruro (ArF) que operan en una longitud de onda de 193 nm. Como resultado, el mayor fabricante de semiconductores por contrato del mundo podrá utilizar las herramientas de fabricación existentes para fabricar chips de 7 nm. Mientras tanto, para continuar utilizando la litografía DUV, la empresa y sus clientes deben utilizar multipastterning (patrones triples y cuádruples), lo que aumenta los costos de diseño y producción, así como los ciclos de los productos.

| Mejoras de PPA anunciadas de las tecnologías de nuevos procesos Datos anunciados por las empresas durante las conferencias telefónicas, informes de prensa y comunicados de prensa |

|||||||

| TSMC | |||||||

| 16FF + vs 20SOC |

10FF vs 16FF + |

7FF vs 16FF + |

7FF vs 10FF |

7FF + vs 7FF |

|||

| Poder | 60% | 40% | 60% | <40% | 10% | ||

| Actuación | 40% | 20% | 30% | ? | mayor | ||

| Reducción de área | ninguna | > 50% | 70% | > 37% | ~ 17% | ||

El próximo año TSMC tiene la intención de presentar su primera tecnología de fabricación que utiliza la litografía ultravioleta extrema (EUVL) para capas seleccionadas. El CLN7FF + es el proceso de fabricación de la segunda generación de 7 nm de la empresa debido a la compatibilidad de las reglas de diseño y porque utiliza las herramientas DUV que utiliza TSMC hoy en día para su producción CLN7FF. Desde un punto de vista general de mejora de la PPA (potencia, rendimiento, área), TSMC espera que su CLN7FF + ofrezca una densidad de transistor 20% más alta y baja de energía un 10% menor con la misma complejidad y frecuencia que el CLN7FF.Además, la tecnología de 7 nm basada en EUV de TSMC también podría ofrecer un mayor rendimiento y una distribución más ajustada de las corrientes, pero los ejecutivos de la compañía no cuantificarán las mejoras en este momento.

"Nuestro resultado de N7 + silicio hoy es muy alentador", dijo el Sr. Wei. "No solo hemos hecho rendimientos equivalentes o superiores de rendimiento [y] tanto en la SRAM de 256 Mb como en el producto como vehículo de prueba en comparación con la línea de base del N7, también hemos probado una distribución más ajustada de parámetros eléctricos en las áreas donde EUV es proporcionado. "

TSMC está en camino de comenzar HVM usando su tecnología de proceso EUV de 7 nm a mediados de 2019. En el futuro, la compañía aumentará el uso de los sistemas de escaneo y escaneo Twinscan NXE de ASML cuando comience a usar su tecnología de proceso CLN5 (5 nm) en 2020. Según el co-CEO de TSMC, los resultados de EUV han sido alentadores. ahora: el chip de prueba SRAM de 256 Mb de la empresa ya está hecho con un "rendimiento consistente de dos dígitos", lo que es bastante bueno para una tecnología que está a dos años de HVM. El alto ejecutivo de TSMC también notó que la infraestructura de EUV en general tuvo un buen progreso en los últimos trimestres.En particular, la compañía de los casinos defectos de la película más bajos, mayores rendimientos de máscara y fotorresistencias mejoradas.

Fuente: Anandtech